1588 Tiny: Slave Only HARD IP Core

|

Overview

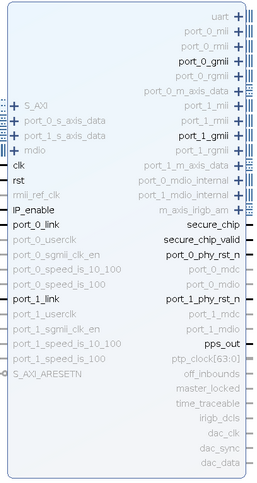

The 1588Tiny is a IEEE1588-2008 V2 Slave Only hard-only compliant clock synchronization IP core for Xilinx FPGAs. It is focused on equipments that requires basic IEEE 1588 functionality using the minimum resources. 1588Tiny is capable of accurately time-stamping IEEE 1588 telegrams and also provides a synchronized clock using only hardware modules.

An embedded processor is not required, nor a generic Ethernet MAC. 1588Tiny includes an optimized Ethernet MAC to process PTP frames. It supports Power Profile and IEC 61850 and it can also support other profiles. The reference design targets AVNET Spartan-6 FPGA LX9 Microboard.

Key Features

- IP core netlist ready for seamless integration in Vivado design flow

- Available profiles: Power, IEC 61850 (Power Utility) and Default

Supported FPGAs

- 6-Series (Spartan, Virtex)

- 7-Series (Zynq, Spartan, Artix, Kintex, Virtex)

- Ultrascale (Kintex, Virtex)

- Ultrascale+ (Zynq MPSoC, Kintex, Virtex)

|

Embedded Development Suite

A hardware development platform is available. Latest documentation, design support files, reference design source files and tools are available for download free of charge.

* Device supported by the free Xilinx Vivado WebPACK tool.

Pricing, Availability and Ordering

- Concurrent EDA is the US Distributor for SoC-e.

- Currently Available to US customers only.

- Please email Ray at

This email address is being protected from spambots. You need JavaScript enabled to view it. with questions / quotes / orders.