Multiport TSN Kit

The Multiport Time Sensitive Networking (MTSN) Switch IP is SoC-e solution for any customer that requires an all-in-one solution to introduce Time Sensitive Networking in their equipment.

The MTSN Switch IP can be implemented optimally depending on the application. It can be configured to generate from a simple 2-ports TSN adaptor to a complex multiport switch. The designer can select, among other parameters, the number of ports and memory distribution for the switch implemented in the FPGA section. This entire configuration is done graphically using Xilinx Vivado Tool.

The MTSN Switch IP can be evaluated using this MTSN Kit. This kit has been designed not only to test the MTSN Switch IP, but to support an advanced hands-on TSN as well. It is composed by two boards ready to run a TSN Network setup.

|

There are two version of the Kit available, one based on Xilinx Zynq-7000 SoC and another one based on Zynq Ultrascale+ MPSoC.

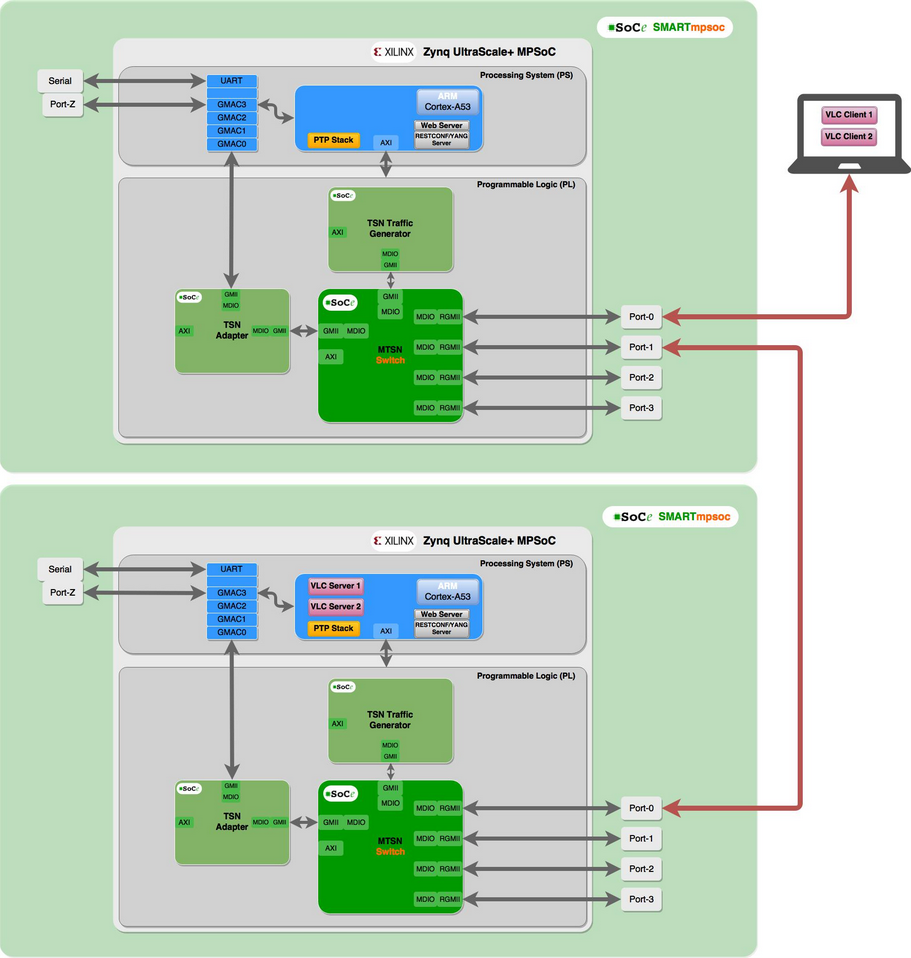

MTSN Kit -MPSoC version-

The block diagram of the design implemented on the MTSN Kit (MPSoC version) is shown in the following figure:

|

The main elements included in this design are:

- PS Section: Processing System section of the SoC

- PL Section: Programmable Logic section of the SoC

- TSN Traffic Generator: HDL Block able to generate different class Ethernet Traffic with controlled throughput. Additionally, it integrates a Time Aware Shaper for scheduling the conventional Ethernet Traffic with controlled throughput. Additionally, it integrates a Time Aware Shaper for scheduling the conventional Ethernet traffic generated by the traffic generator block.

- TSN Adapter: HDL Block in charge of implementing the Time Aware Shaper for scheduling the conventional Ethernet traffic managed by the standard regular Ethernet MAC of the Processor Section of the SoC.

- MTSN Switch IP: Six-ports TSN switch. These ports are distributed as two internal and four external ports.

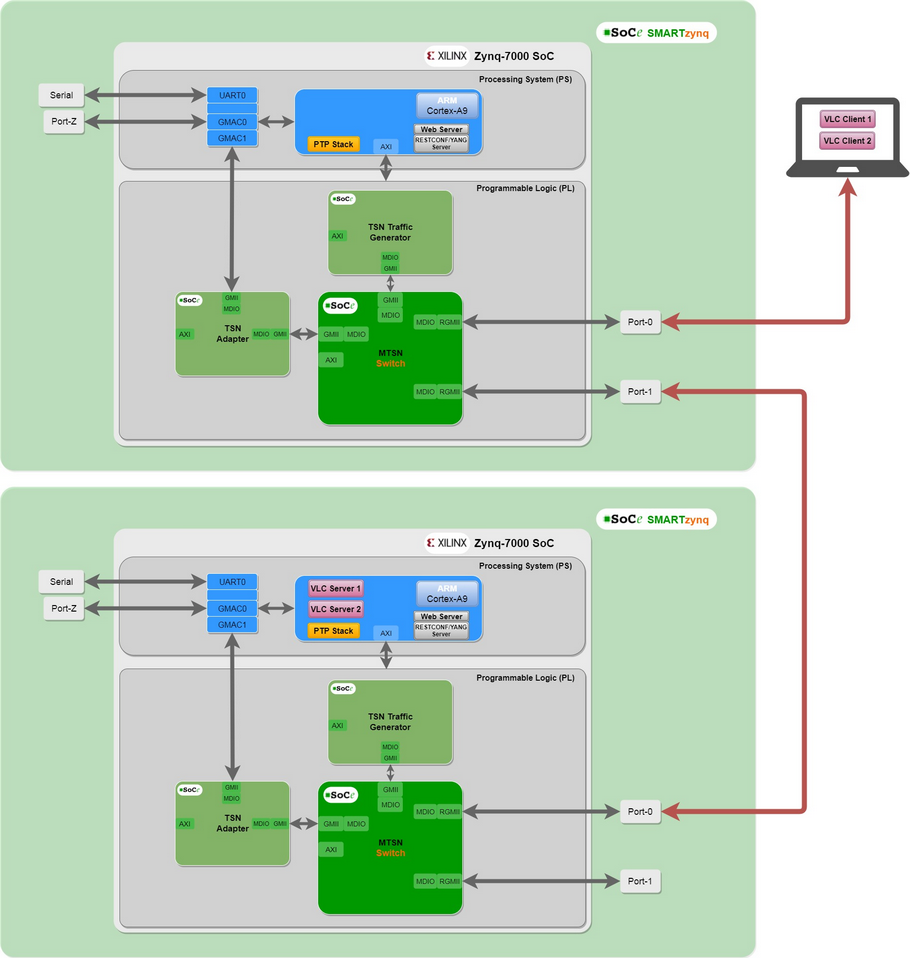

MTSN Kit - Zynq version -

The block diagram of the design implemented on MTSN Kit (Zynq version) is shown in the following figure:

|

The main elements included in this design are:

- PS Section: Processing System section of the SoC.

- PL Section: Programmable Logic section of the SoC.

- TSN Traffic Generator: HDL Block able to generate different class Ethernet Traffic with controlled throughput. Additionally, it integrates a Time Aware Shaper for scheduling the conventional Ethernet traffic generated by the traffic generator block.

- TSN Adapter: HDL Block in charge of implementing the Time Aware Shaper for scheduling the conventional Ethernet traffic managed by the standard regular Ethernet MAC of the Processor Section of the SoC.

- MTSN Switch IP: Four-ports TSN switch. These ports are distributed as two internal and two external ports

|

Package Contents

Zynq Version

- 2x SMARTzynq boards pre-loaded with TSN Evaluation Design

- 2x SMARTzynq Power Supplies

- 4x Tri-speed Ethernet Copper SFPs

- 2x USB cables

MPSoC Version

- 2x SMARTzynq boards pre-loaded with TSN Evaluation Design

- 2x SMARTzynq Power Supplies

- 8x Tri-speed Ethernet Copper SFPs

- 2x USB cables

Pricing, Availability and Ordering

- Concurrent EDA is the US Distributor for SoC-e products.

- Currently Available to US customers only.

- Please email Ray at

This email address is being protected from spambots. You need JavaScript enabled to view it. with questions / quotes / orders.