IRIG-B Master Core

|

Overview

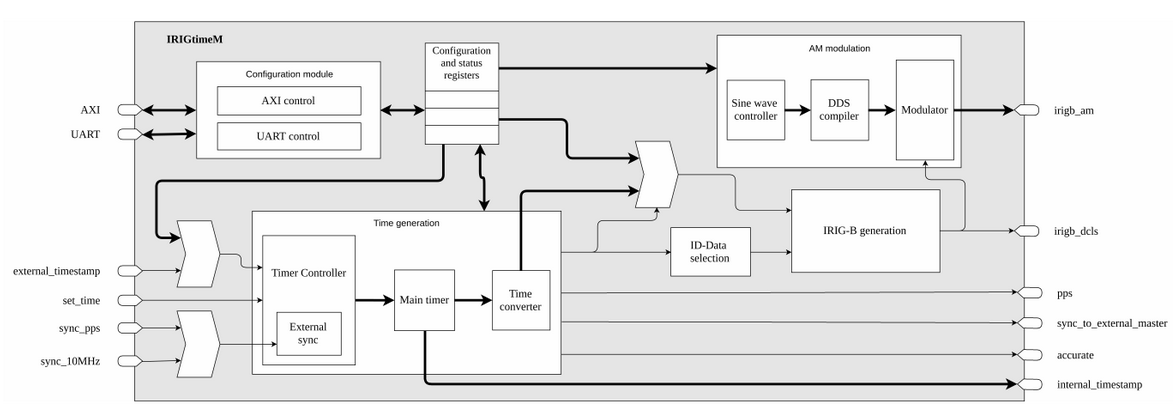

The IRIGtimeM IP Core implements an IRIG 200-04 compliant time synchronization master on FPGA devices. This IRIG-B master IP has been designed to support all the IRIG-B coded expressions as well as DCLS and AM modulations in order to provide maximum flexibility.

This IRIG-B master IP generates IRIG-B frames each second, including the mandatory and optional time information (seconds, minutes, hours, days, years, control functions and binary straight seconds) depending on the IRIG-B time code selected on the configuration. This IP has been designed to provide autonomous operation, requiring as less configuration as possible.

Key Features

- IRIG 200-04 compliant time synchronization master

- Support for DCLS and AM modulations

- Support for all IRIG-B coded expressions, including year information, control functions and straight binary seconds

- Output type (IRIG-B timecode) configurable both before implementation and on the fly

- Precise IRIG-B output in order to provide nanoseconds precision

- 32-bit timestamp input for initial set up of the IP

- Periodic pulse output for testing

|

Supported FPGAs

- 6-Series (Spartan, Virtex)

- 7-Series (Zynq, Spartan, Artix, Kintex, Virtex)

- Ultrascale (Kintex, Virtex)

- Ultrascale+ (Zynq MPSoC, Kintex, Virtex)

Embedded Development Suite

A hardware development platform is available. Latest documentation, design support files, reference design source files and tools are available for download free of charge.

* Device supported by the free Xilinx Vivado WebPACK tool.

Pricing, Availability and Ordering

- Concurrent EDA is the US Distributor for SoC-e.

- Currently Available to US customers only.

- Please email Ray at

This email address is being protected from spambots. You need JavaScript enabled to view it. with questions / quotes / orders.